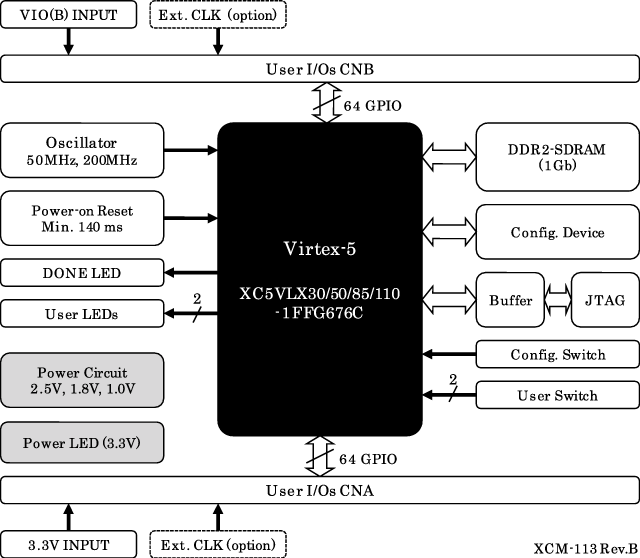

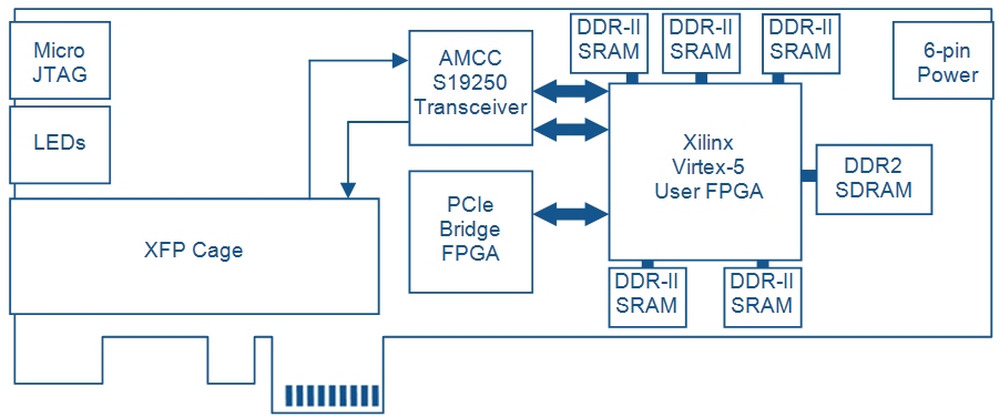

Virtex 5 Block Diagram

Vcc33 vcco0 vcc3en vcctmp vcco0 vcc33 vcco0.

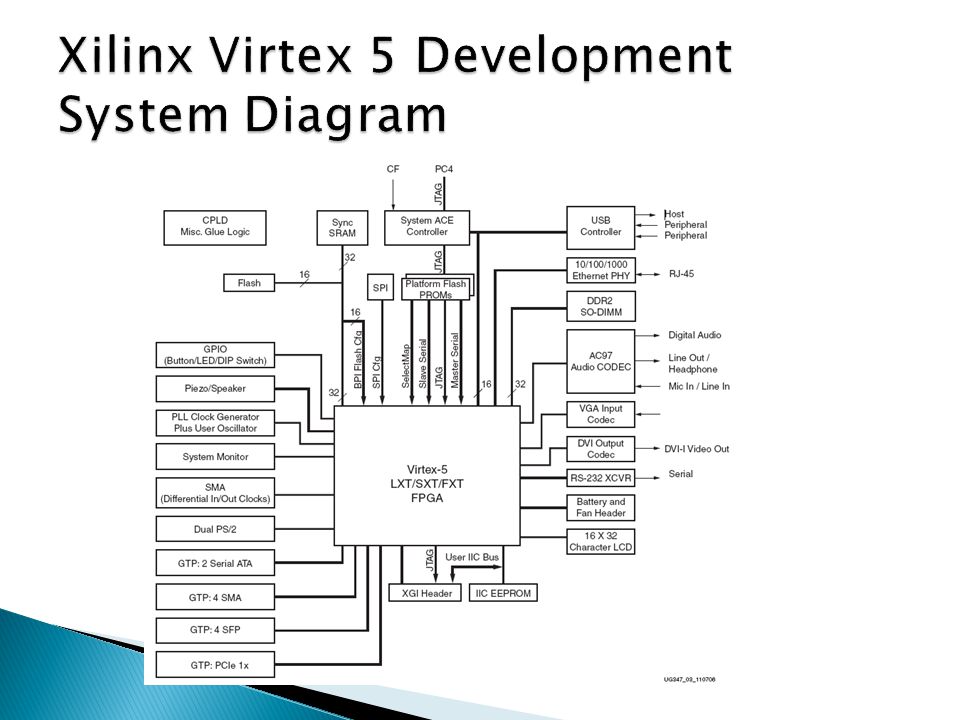

Virtex 5 block diagram. One reference system is based on the powerpc 440 ppc440 processor and the other reference system is based on the microblaze processor. 29 art pn 0531591 fab pn 1280403 sch pn 0381232 schem rohs compliant virtex 5 ff1760 daughter 01 b. Supports endpoint to root complex dma full duplex read and write transactions initiated by. The reference design runs on the virtex 5 fpga ml555 development board for pci express designs.

When bufio and bufr are used to generate the serial and parallel clocks the phase relationship between the two clocks is guaranteed by design to meet the input requirements of the oserdes and iserdes. 25 art pn 0531590 01 fab pn 1280402 01 sch pn 0381231 01 schemrohs compliant virtex 5 ff1153 daughter 1280402 01 b. The virtex 5 fxt development kit includes two reference systems that target the ml507 development board. Virtex 5 fpga integrated endpoint block for pci express designs and a single rank 64 bit 256 mb ddr2 sdram memory.

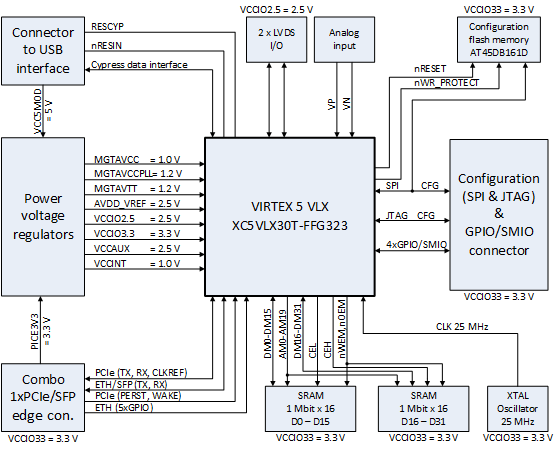

Virtex 5 fpga integrated endpoint block user guide for pci express designs this guide describes the integrated endpoint blocks in the virtex 5 lxt sxt txt and fxt platforms used for pci express designs. A high level block diagram of the virtex 5 lx evaluation board is shown below followed by a brief description of each sub section. Vcc33 vcco0 vcc3en vcctmp vcco0. 17 art pn 0531589 01 fab pn 1280401 01 sch pn 0381320 01 schemrohs compliant virtex 5 ff324 daughter 1280401 01 b.

In the block diagram of the ddr transmitter shown in figure 5 page 5 the clock networks are shown driven by bufio and bufr. Virtex 5 dut init led user leds program user reset jack brick done switches jtag all dut io test points page 2 page 2 page 2 page 2 page 2 page 5 page 5 page 5 page 3.